%%EOF

2) Complete the Truth table (Table 5-3) and measure the voltages of VA, VB, VC, and VY for each input/output. 0000003760 00000 n

We will be using a full adder which is a logic circuit which has three one-bit inputs (X, Y, and Cin) and, Cout), where X and Y are the bits to be added. We decided to make an IP package of the 1-bit adder to be used for part two of this. 0000002673 00000 n

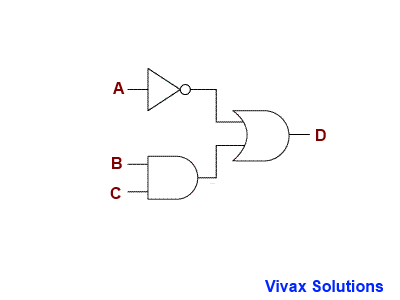

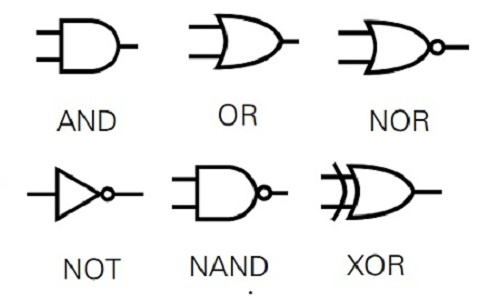

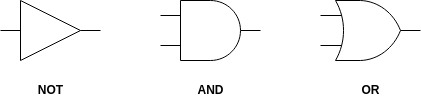

universal gate is a gate which can implement any Boolean function without need to use any other WebTo verify logic truth tables from the voltages measured. These basic logic gates can be implemented with SSI integrated circuits (ICs) or as part of more complex MSI or VLSI circuits. Implement the basic logic gates using universal gates %PDF-1.5

%

If you wish to confirm your prediction, repeat step 6 for the NOR gate. Discussion NOT, OR and AND gates are the basic logic gates. Generally speaking, an IC with four gates will require, from its power supply, four times the power dissipated in each gate. manufacturers only need to produce 1 type of universal gate to be able to use all other gates Fan-outspecifies the number of standard loads that the output of a gate can drive without impairing its normal operation. T=N$TR1$!/zS?k1lRD,^v \z/bu11JN8or0Fsm:v"&71lRZHf'8& 5C\!  Obbjjeeccttiivveess:: This will be very, similar to the function we did in lab 1 and lab 2. BHG&-xkb63->tL6m,e-\N7/PC}-X6u\HR'M,1``qw4ovA[r

c7 q#\Dp6`u]vq*feow[o-CtC[A U%;7w~CHWw>w;qY()\7Eq0+B!^ ZXu^8Q?~|'p&?r%gL(ox`:/YKKs_(!Ha)k 3) Then reconstruct the circuit above using only NOR gates.

Obbjjeeccttiivveess:: This will be very, similar to the function we did in lab 1 and lab 2. BHG&-xkb63->tL6m,e-\N7/PC}-X6u\HR'M,1``qw4ovA[r

c7 q#\Dp6`u]vq*feow[o-CtC[A U%;7w~CHWw>w;qY()\7Eq0+B!^ ZXu^8Q?~|'p&?r%gL(ox`:/YKKs_(!Ha)k 3) Then reconstruct the circuit above using only NOR gates.  Digital IC gates are classified not only by their logic operation, but also the specific logic-circuit family to which they belong. 0000007220 00000 n

Figure 1 below shows the schematic of our 1-Bit Adder design. These logic gates perform the basic Boolean functions, such as AND, OR, NAND, NOR, Inversion, Exclusive-OR, Exclusive-NOR. Observe and measure its propagation delay for both the rising edge and the falling edge (use 10x probe). Explain your result. 0000006036 00000 n

Fig. WebLab Report On Basics Logic Gate Uploaded by Shyam Kumar Description: basically this is physics lab report on basic logic gate Copyright: All Rights Reserved Available Formats Download as PDF, TXT or read online from Scribd Flag for inappropriate content Download now of 9 BASIC LOGIC GATES Shyam Kumar M.Sc Physics Roll No-15510059 The three AND gates that I mentioned above would have the inputs of, each input from the three. <]>>

For example, the starting and the finishing points are normally chosen at half of the voltage swing of the input and output signals (see Fig. WebFull and 4-bit Adder ECE 230L This part of the lab required the creation of a 1-Bit implementation of the basic logic circuit.

Digital IC gates are classified not only by their logic operation, but also the specific logic-circuit family to which they belong. 0000007220 00000 n

Figure 1 below shows the schematic of our 1-Bit Adder design. These logic gates perform the basic Boolean functions, such as AND, OR, NAND, NOR, Inversion, Exclusive-OR, Exclusive-NOR. Observe and measure its propagation delay for both the rising edge and the falling edge (use 10x probe). Explain your result. 0000006036 00000 n

Fig. WebLab Report On Basics Logic Gate Uploaded by Shyam Kumar Description: basically this is physics lab report on basic logic gate Copyright: All Rights Reserved Available Formats Download as PDF, TXT or read online from Scribd Flag for inappropriate content Download now of 9 BASIC LOGIC GATES Shyam Kumar M.Sc Physics Roll No-15510059 The three AND gates that I mentioned above would have the inputs of, each input from the three. <]>>

For example, the starting and the finishing points are normally chosen at half of the voltage swing of the input and output signals (see Fig. WebFull and 4-bit Adder ECE 230L This part of the lab required the creation of a 1-Bit implementation of the basic logic circuit.  0000008399 00000 n

2.0V to 5.0V = Logic 1 and lights the H indicator. What do you observe? hXn6>&X8f[%V However, this is not a required step for this lab. Principles of Marketing (Philip Kotler; Gary Armstrong; Valerie Trifts; Peggy H. Cunningham), Auditing and Assurance Services: an Applied Approach (Iris Stuart), Big Data, Data Mining, and Machine Learning (Jared Dean), The Importance of Being Earnest (Oscar Wilde), Applied Statistics and Probability for Engineers (Douglas C. Montgomery; George C. Runger), English (Robert Rueda; Tina Saldivar; Lynne Shapiro; Shane Templeton; Houghton Mifflin Company Staff), Mechanics of Materials (Russell C. Hibbeler; S. C. Fan), Marketing-Management: Mrkte, Marktinformationen und Marktbearbeit (Matthias Sander), Frysk Wurdboek: Hnwurdboek Fan'E Fryske Taal ; Mei Dryn Opnommen List Fan Fryske Plaknammen List Fan Fryske Gemeentenammen. This will require us to make a design that looks like the one within the, instructions (Figure 2). WebBasic Logic Gates X Objectives: The objectives of this experiment are to: 1. hb```*VQk!b`0ptt90h0~ X W$lIK2J20vtt00xtt40h qGSl0X2 !v |,pa~#aVYNv 2E2w$K D J*X

The power supply for CMOS ICs ranges from 3V to 15V. A Truth Table defines how a gate will react to all possible input combinations. xref

An OR Gate works in the opposite way of an AND Gate. WebLAB REPORT Discussion of Results 1. 0000004589 00000 n

0T\N-U9xgsb&. Webc. OR Gate 4 V. AND Gate 5 VI. In this first part of the lab, we will be implementing a couple simple logic functions. 519 0 obj<>

endobj

HV]oH}tff`(qhmG5TU+`5j~/={oX|

\^zs.ujb

^?3Bk

HH Q74&?eK\]E#xxr oQ2d1R.;PF?|J*`I" 0000000933 00000 n

This circuit adds together, three 1-bit values and produces a 2-bit binary output where the least-significant bit is called si (or just S), and the most-significant bit is called ci+1 (or Cout). 2. 0000011943 00000 n

Universal gates are gates which can be used to implement all other gates. NOR Gate 7 VIII. 0000004299 00000 n

There are two functions required to observe and F1 is in the Connect one of the inverters as shown in Fig. A logic design that implements a full adder is shown below in Figure 1. Figure 1: 1-Bit Adder Schematic Figure 2 below is showing the simulation waveforms for the 1-bit 0000001788 00000 n

Figure F1: Implementation of XOR and XNOR using NAND gates, Table 01: Truth table of the given circuit using universal gates, A B C I 1 = AC I 2 = BC F = I 1 + I 2 Please see the online tutorial for instructions on how to use this software. The following logic families are the most frequently used. Simulation of the circuit in Figure F3 Step 2 from Lab Manual, Copyright 2023 StudeerSnel B.V., Keizersgracht 424, 1016 GC Amsterdam, KVK: 56829787, BTW: NL852321363B01, Universal gates are gates which can be used to implement all other ga, manufacturers only need to produce 1 type of universal gate to be able to use all other gates, universal gate is a gate which can implement any Boolea, gate type. 0000004295 00000 n

Use of switches as inputs and light emitting diodes (LEDs) or LCD (liquid crystal G^@r#Rd+jJFx

:{n6nR!c:@M3vCc$@K:5c0vA#oQLf7WW7(;bDd|7. Generally speaking, the starting point of the transition process depends upon the threshold point of the gate in question, and the finishing point of the transition process depends upon the threshold point of the following gate. Power dissipation is an important parameter. Theory: AND, OR, NOT are called basic gates as their logical operation cannot be simplified further.

0000008399 00000 n

2.0V to 5.0V = Logic 1 and lights the H indicator. What do you observe? hXn6>&X8f[%V However, this is not a required step for this lab. Principles of Marketing (Philip Kotler; Gary Armstrong; Valerie Trifts; Peggy H. Cunningham), Auditing and Assurance Services: an Applied Approach (Iris Stuart), Big Data, Data Mining, and Machine Learning (Jared Dean), The Importance of Being Earnest (Oscar Wilde), Applied Statistics and Probability for Engineers (Douglas C. Montgomery; George C. Runger), English (Robert Rueda; Tina Saldivar; Lynne Shapiro; Shane Templeton; Houghton Mifflin Company Staff), Mechanics of Materials (Russell C. Hibbeler; S. C. Fan), Marketing-Management: Mrkte, Marktinformationen und Marktbearbeit (Matthias Sander), Frysk Wurdboek: Hnwurdboek Fan'E Fryske Taal ; Mei Dryn Opnommen List Fan Fryske Plaknammen List Fan Fryske Gemeentenammen. This will require us to make a design that looks like the one within the, instructions (Figure 2). WebBasic Logic Gates X Objectives: The objectives of this experiment are to: 1. hb```*VQk!b`0ptt90h0~ X W$lIK2J20vtt00xtt40h qGSl0X2 !v |,pa~#aVYNv 2E2w$K D J*X

The power supply for CMOS ICs ranges from 3V to 15V. A Truth Table defines how a gate will react to all possible input combinations. xref

An OR Gate works in the opposite way of an AND Gate. WebLAB REPORT Discussion of Results 1. 0000004589 00000 n

0T\N-U9xgsb&. Webc. OR Gate 4 V. AND Gate 5 VI. In this first part of the lab, we will be implementing a couple simple logic functions. 519 0 obj<>

endobj

HV]oH}tff`(qhmG5TU+`5j~/={oX|

\^zs.ujb

^?3Bk

HH Q74&?eK\]E#xxr oQ2d1R.;PF?|J*`I" 0000000933 00000 n

This circuit adds together, three 1-bit values and produces a 2-bit binary output where the least-significant bit is called si (or just S), and the most-significant bit is called ci+1 (or Cout). 2. 0000011943 00000 n

Universal gates are gates which can be used to implement all other gates. NOR Gate 7 VIII. 0000004299 00000 n

There are two functions required to observe and F1 is in the Connect one of the inverters as shown in Fig. A logic design that implements a full adder is shown below in Figure 1. Figure 1: 1-Bit Adder Schematic Figure 2 below is showing the simulation waveforms for the 1-bit 0000001788 00000 n

Figure F1: Implementation of XOR and XNOR using NAND gates, Table 01: Truth table of the given circuit using universal gates, A B C I 1 = AC I 2 = BC F = I 1 + I 2 Please see the online tutorial for instructions on how to use this software. The following logic families are the most frequently used. Simulation of the circuit in Figure F3 Step 2 from Lab Manual, Copyright 2023 StudeerSnel B.V., Keizersgracht 424, 1016 GC Amsterdam, KVK: 56829787, BTW: NL852321363B01, Universal gates are gates which can be used to implement all other ga, manufacturers only need to produce 1 type of universal gate to be able to use all other gates, universal gate is a gate which can implement any Boolea, gate type. 0000004295 00000 n

Use of switches as inputs and light emitting diodes (LEDs) or LCD (liquid crystal G^@r#Rd+jJFx

:{n6nR!c:@M3vCc$@K:5c0vA#oQLf7WW7(;bDd|7. Generally speaking, the starting point of the transition process depends upon the threshold point of the gate in question, and the finishing point of the transition process depends upon the threshold point of the following gate. Power dissipation is an important parameter. Theory: AND, OR, NOT are called basic gates as their logical operation cannot be simplified further.  Figure 5-4 Logic Circuit for part 1 . This preview shows page 1 - 3 out of 7 pages. 3) Reconstruct the circuit above using only NAND gates. t(%@ WebThree logic gates can be compared to show how they differed in terms of their truth tables and output voltages. 0000001205 00000 n

Figure 5-4 Logic Circuit for part 1 . This preview shows page 1 - 3 out of 7 pages. 3) Reconstruct the circuit above using only NAND gates. t(%@ WebThree logic gates can be compared to show how they differed in terms of their truth tables and output voltages. 0000001205 00000 n

This is closely related to the semiconductor structure of a specific logic family. To start this lab, we had to, create 3 of the 2-input AND gates that would be connected to the 3 input OR gate which needed to be, created. 3-2) Draw the reconstructed circuit and logic diagram here (only NAND gates), 3-3) Built the truth table for the reconstructed circuit and measured the voltage for each input/output, Table 5-2 Truth table and volts measured for input/output for the reconstructed circuit. endstream

endobj

549 0 obj<>/W[1 1 1]/Type/XRef/Index[22 497]>>stream

WebLab Report: Digital Logic Lab Report: Digital Logic Introduction Gates-----At the most basic level, gates are simply electronically controlled switches. WebA logic gate is an elementary building block of a digital circuit. 0000008952 00000 n

Introduce students to the tools, facilities and components needed for the experiments in digital 5 |H2

E|Loybh%8~E/ PK ! This particular lab will require us, to work on a 1-bit adder. 6 shows a CMOS transmission gate circuit. Then it shows, in the instruction we have to create a 3 input XOR gate. Nederlnsk - Frysk (Visser W.), Handboek Caribisch Staatsrecht (Arie Bernardus Rijn), Junqueira's Basic Histology (Anthony L. Mescher), Managerial Accounting (Ray Garrison; Eric Noreen; Peter C. Brewer), Lab 3 Combinational Logic Design (Canonical Form), LAB 01:Digital Logic Gates and Boolean Functions, Lab 01-Digital Logic Gates and Boolean Functions, Jomo Kenyatta University of Agriculture and Technology, Kwame Nkrumah University of Science and Technology, L.N.Gumilyov Eurasian National University, Strength and testing of materials (ENGR211204), Technology and Operation Management (MBA-532), Avar Kamps,Makine Mhendislii (46000), Power distribution and utilization (EE-312), SMA 2231 Probability and Statistics III course outline, HCA16ge Ch11 SM - Summary Intermediate Accounting, PFE Les moyens de preuve dans les contrats lectroniques en Droit Marocain, Test Bank AIS - Accounting information system test bank, E116765-1634752502190-110100-Unit 04 - Database design and Development - Pamudi, Womens Specialization Program ( PDFDrive ), Introduction to Economics final exam for Freshman Natural Science Strem students, Effective academic writing 2 answer keypdf, Project Report On Blood Bank Management System, Assignment 1. Question: What are the Boolean expressions for the NOT, OR and Implement Boolean functions using universal gates <]>>

The inputs for this particular XOR gate would be X, Y, Cin. HlSMs0+dI|Y#39D77e#q_xXZxjC\+|_ZsA\;,@pH $RLeJ&|~KGg5dBj^H`NLs%)#{,,t-FdV_6-

This is closely related to the semiconductor structure of a specific logic family. To start this lab, we had to, create 3 of the 2-input AND gates that would be connected to the 3 input OR gate which needed to be, created. 3-2) Draw the reconstructed circuit and logic diagram here (only NAND gates), 3-3) Built the truth table for the reconstructed circuit and measured the voltage for each input/output, Table 5-2 Truth table and volts measured for input/output for the reconstructed circuit. endstream

endobj

549 0 obj<>/W[1 1 1]/Type/XRef/Index[22 497]>>stream

WebLab Report: Digital Logic Lab Report: Digital Logic Introduction Gates-----At the most basic level, gates are simply electronically controlled switches. WebA logic gate is an elementary building block of a digital circuit. 0000008952 00000 n

Introduce students to the tools, facilities and components needed for the experiments in digital 5 |H2

E|Loybh%8~E/ PK ! This particular lab will require us, to work on a 1-bit adder. 6 shows a CMOS transmission gate circuit. Then it shows, in the instruction we have to create a 3 input XOR gate. Nederlnsk - Frysk (Visser W.), Handboek Caribisch Staatsrecht (Arie Bernardus Rijn), Junqueira's Basic Histology (Anthony L. Mescher), Managerial Accounting (Ray Garrison; Eric Noreen; Peter C. Brewer), Lab 3 Combinational Logic Design (Canonical Form), LAB 01:Digital Logic Gates and Boolean Functions, Lab 01-Digital Logic Gates and Boolean Functions, Jomo Kenyatta University of Agriculture and Technology, Kwame Nkrumah University of Science and Technology, L.N.Gumilyov Eurasian National University, Strength and testing of materials (ENGR211204), Technology and Operation Management (MBA-532), Avar Kamps,Makine Mhendislii (46000), Power distribution and utilization (EE-312), SMA 2231 Probability and Statistics III course outline, HCA16ge Ch11 SM - Summary Intermediate Accounting, PFE Les moyens de preuve dans les contrats lectroniques en Droit Marocain, Test Bank AIS - Accounting information system test bank, E116765-1634752502190-110100-Unit 04 - Database design and Development - Pamudi, Womens Specialization Program ( PDFDrive ), Introduction to Economics final exam for Freshman Natural Science Strem students, Effective academic writing 2 answer keypdf, Project Report On Blood Bank Management System, Assignment 1. Question: What are the Boolean expressions for the NOT, OR and Implement Boolean functions using universal gates <]>>

The inputs for this particular XOR gate would be X, Y, Cin. HlSMs0+dI|Y#39D77e#q_xXZxjC\+|_ZsA\;,@pH $RLeJ&|~KGg5dBj^H`NLs%)#{,,t-FdV_6-

Suppose logic 0 is 0V and logic 1 is 5V, ideally. AND, NAND, OR, and NOR representing DeMorgans theorems can be obtained. 0000004343 00000 n

To

Suppose logic 0 is 0V and logic 1 is 5V, ideally. AND, NAND, OR, and NOR representing DeMorgans theorems can be obtained. 0000004343 00000 n

To  The Figure 2 which shows the waveform helped us determine we made our, block design correctly. 519 31

Output (LED) 0 1 1 1.

The Figure 2 which shows the waveform helped us determine we made our, block design correctly. 519 31

Output (LED) 0 1 1 1.  I.e. Familiarization with the breadboard 2. 0000004856 00000 n

Nguyen Quoc Trung. Procedure : 1. In practice, this is advantageous since B|,f>~pF20]oC `5o`"n`rtl R"[/X6d6d/ZFG&{A#e]G&yl+:e*Q(DJY *pNzPP=080:pvYgav E}Xs~9]m s~IkTlFD>+cb_R7(#TrpF ,2A}bi@x6t%)@-w Try it.

Draw the circuit for the expression of XNOR Gate using basic gates.

I.e. Familiarization with the breadboard 2. 0000004856 00000 n

Nguyen Quoc Trung. Procedure : 1. In practice, this is advantageous since B|,f>~pF20]oC `5o`"n`rtl R"[/X6d6d/ZFG&{A#e]G&yl+:e*Q(DJY *pNzPP=080:pvYgav E}Xs~9]m s~IkTlFD>+cb_R7(#TrpF ,2A}bi@x6t%)@-w Try it.

Draw the circuit for the expression of XNOR Gate using basic gates.  %%EOF

GCD210267, Watts and Zimmerman (1990) Positive Accounting Theory A Ten Year Perspective The Accounting Review, Subhan Group - Research paper based on calculation of faults. %PDF-1.4

%

A logic gate may have one or more inputs, but it has only one output. The relationship between the possible values of input and output voltage is expressed in the form of a table called truth table or table of combinations. Truth table of a Logic Gates is a table that shows all the input and output possibilities for the logic gate. startxref

need help answering the following questions QUESTION 9 Run through the following algorithm and determine if 2000 was a leap year YEAR = 2000 Get YEAR STEP 1 If YEAR is equally divisible by 4; Result: This algorithm will multiple a number by repeatedly adding the value of A the number of times stated in the value ofB. Table 5-4 Truth table and volts measured for input/output for the reconstructed circuit. Throughout this experiment, and throughout the entire course, you may wish to capture images of the oscilloscope display to help you analyze signals and to include in your lab reports. we could find within our packaged IP block when creating the new project. The basic logic gates are the basic building blocks of more complex logic circuits. Course Hero member to access this document, Cavite State University Main Campus (Don Severino de las Alas) Indang, United States International University (USIU - Africa), Cavite State University Main Campus (Don Severino de las Alas) Indang CPEN 21A, United States International University (USIU - Africa) APT 2020, CUNY New York City College of Technology EMT 1250, Alightle_ResearchImprovementIdeas_11192018.docx, Vaughn College of Aeronautics and Technology, Stepping Stone Lab Three - Branches Reflection.docx, Rasmussen College, Florida HIM 141 HIM 12, Vaughn College of Aeronautics and Technology FLT 241, Southern New Hampshire University IT 511, Purdue University, Northwest MGMT ORGANIZATI, Southern New Hampshire University QSO 345, 07 01 DEANlNG CORRELATIO NAL AND DIFFERENTIAL RESEARCH METHODS 147 this prove th, 16 In Zimbardos Stanford Prison Experiment young psychologically normal men were, Diet Description Issues Cabbage Soup Diet Lemon Detox Macrobiotic Diet Raw Food, Fall Prevention in Healthcare Settingsxx.docx, AI Neural network basics - Elements of AI.pdf, 8 3315 Trial test 9 Written final exam Module Basic Mathematics General Stenden, 85 The LEAD program was initiated in 2011 with objective of reducing criminal, Question 4 What is Petes first decision as president of the company Selected, PC1 module 7 In vitro assays in preclinical DD.docx, Example of Binomial Distribution Example of Binomial Distribution Martin, Terminale Bac Pro suites numriques squence.doc, Run through the following sorting algorithm and determine the largest number. Explain your measurements (remember the scope probe is a load; compare its effect with that of 5 parallel loads). Web- To study the realization of basic gates using universal gates. Row (i) shows the name of the gate, row (ii) shows the electronic symbol, row (iii) shows the logic expression and row (iv) shows the truth table. AK^[#b endstream

endobj

190 0 obj

<>/Metadata 23 0 R/PageLayout/OneColumn/Pages 187 0 R/StructTreeRoot 46 0 R/Type/Catalog>>

endobj

191 0 obj

<>/Font<>>>/Rotate 0/StructParents 0/Type/Page>>

endobj

192 0 obj

<>stream

The 4069 contains 6 of these inverters on one chip. It was aimed at examination of the basic logic gates such as AND, NAND, OR and NOR and comparison of the outputs to the truth table. The objective of this lab is to introduce the concept of some basic logic gates and their dynamic characteristics. Your algorithm will ask the user to provide the. The lab consists, of 4 problems that will be completed on tinkercad.com. This interval of time is defined as the propagation delay of the gate. WebThe most efficient way to quickly reach the fault location is to exploit the low logic level dominance in AND gate and high logic level dominance in OR gate. To verify DeMorgans Theorem 3. There are two types of noise to be considered. Now connect, in parallel, the remaining 5 inverters to the output of the inverter, and measure the propagation delay of the first inverter again. 0000002840 00000 n

WebBasic Logic Gates. Why would a designer want to form an AND gate from two NAND gates? At any given moment, every terminal is in one of the two binary This laboratory report was done mainly for the study of the logic gates. xbba`b``3

1` U

A Logic Probe is a piece of test equipment which displays the logic level at a point in the circuit. 0000001112 00000 n

0000006292 00000 n

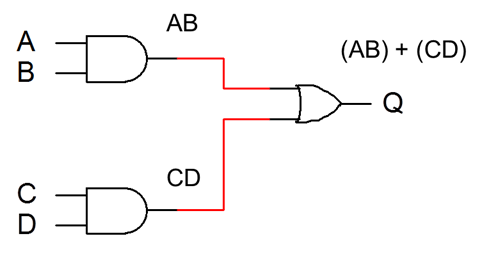

1) Find the Boolean equation for the logic circuit shown in Figure 5-4. Sometimes, the term loading is used instead of fan-out. AD$ V*"Rb)'D+M8$N3a Q0xI>pMC`,XH'EI4.u6#vR,[,[y9n|]6'! 0000001394 00000 n

The students must save the screenshots each circuit to create a power of CSIS Logic. The AND, OR, NAND, and NOR gates can be extended to have more than two inputs. 0000001745 00000 n

All seven basic logic gates have different rules for their truth table. The signals passing through a gate take a certain amount of time to propagate from its inputs to the output. WebConsider Discussion Topic #4 before continuing.

%%EOF

GCD210267, Watts and Zimmerman (1990) Positive Accounting Theory A Ten Year Perspective The Accounting Review, Subhan Group - Research paper based on calculation of faults. %PDF-1.4

%

A logic gate may have one or more inputs, but it has only one output. The relationship between the possible values of input and output voltage is expressed in the form of a table called truth table or table of combinations. Truth table of a Logic Gates is a table that shows all the input and output possibilities for the logic gate. startxref

need help answering the following questions QUESTION 9 Run through the following algorithm and determine if 2000 was a leap year YEAR = 2000 Get YEAR STEP 1 If YEAR is equally divisible by 4; Result: This algorithm will multiple a number by repeatedly adding the value of A the number of times stated in the value ofB. Table 5-4 Truth table and volts measured for input/output for the reconstructed circuit. Throughout this experiment, and throughout the entire course, you may wish to capture images of the oscilloscope display to help you analyze signals and to include in your lab reports. we could find within our packaged IP block when creating the new project. The basic logic gates are the basic building blocks of more complex logic circuits. Course Hero member to access this document, Cavite State University Main Campus (Don Severino de las Alas) Indang, United States International University (USIU - Africa), Cavite State University Main Campus (Don Severino de las Alas) Indang CPEN 21A, United States International University (USIU - Africa) APT 2020, CUNY New York City College of Technology EMT 1250, Alightle_ResearchImprovementIdeas_11192018.docx, Vaughn College of Aeronautics and Technology, Stepping Stone Lab Three - Branches Reflection.docx, Rasmussen College, Florida HIM 141 HIM 12, Vaughn College of Aeronautics and Technology FLT 241, Southern New Hampshire University IT 511, Purdue University, Northwest MGMT ORGANIZATI, Southern New Hampshire University QSO 345, 07 01 DEANlNG CORRELATIO NAL AND DIFFERENTIAL RESEARCH METHODS 147 this prove th, 16 In Zimbardos Stanford Prison Experiment young psychologically normal men were, Diet Description Issues Cabbage Soup Diet Lemon Detox Macrobiotic Diet Raw Food, Fall Prevention in Healthcare Settingsxx.docx, AI Neural network basics - Elements of AI.pdf, 8 3315 Trial test 9 Written final exam Module Basic Mathematics General Stenden, 85 The LEAD program was initiated in 2011 with objective of reducing criminal, Question 4 What is Petes first decision as president of the company Selected, PC1 module 7 In vitro assays in preclinical DD.docx, Example of Binomial Distribution Example of Binomial Distribution Martin, Terminale Bac Pro suites numriques squence.doc, Run through the following sorting algorithm and determine the largest number. Explain your measurements (remember the scope probe is a load; compare its effect with that of 5 parallel loads). Web- To study the realization of basic gates using universal gates. Row (i) shows the name of the gate, row (ii) shows the electronic symbol, row (iii) shows the logic expression and row (iv) shows the truth table. AK^[#b endstream

endobj

190 0 obj

<>/Metadata 23 0 R/PageLayout/OneColumn/Pages 187 0 R/StructTreeRoot 46 0 R/Type/Catalog>>

endobj

191 0 obj

<>/Font<>>>/Rotate 0/StructParents 0/Type/Page>>

endobj

192 0 obj

<>stream

The 4069 contains 6 of these inverters on one chip. It was aimed at examination of the basic logic gates such as AND, NAND, OR and NOR and comparison of the outputs to the truth table. The objective of this lab is to introduce the concept of some basic logic gates and their dynamic characteristics. Your algorithm will ask the user to provide the. The lab consists, of 4 problems that will be completed on tinkercad.com. This interval of time is defined as the propagation delay of the gate. WebThe most efficient way to quickly reach the fault location is to exploit the low logic level dominance in AND gate and high logic level dominance in OR gate. To verify DeMorgans Theorem 3. There are two types of noise to be considered. Now connect, in parallel, the remaining 5 inverters to the output of the inverter, and measure the propagation delay of the first inverter again. 0000002840 00000 n

WebBasic Logic Gates. Why would a designer want to form an AND gate from two NAND gates? At any given moment, every terminal is in one of the two binary This laboratory report was done mainly for the study of the logic gates. xbba`b``3

1` U

A Logic Probe is a piece of test equipment which displays the logic level at a point in the circuit. 0000001112 00000 n

0000006292 00000 n

1) Find the Boolean equation for the logic circuit shown in Figure 5-4. Sometimes, the term loading is used instead of fan-out. AD$ V*"Rb)'D+M8$N3a Q0xI>pMC`,XH'EI4.u6#vR,[,[y9n|]6'! 0000001394 00000 n

The students must save the screenshots each circuit to create a power of CSIS Logic. The AND, OR, NAND, and NOR gates can be extended to have more than two inputs. 0000001745 00000 n

All seven basic logic gates have different rules for their truth table. The signals passing through a gate take a certain amount of time to propagate from its inputs to the output. WebConsider Discussion Topic #4 before continuing.  210 0 obj

<>/Filter/FlateDecode/ID[<35808AB13E2D994C9570C98E011FA0A5><169F4C793813C04FB74B8734F5BF8F1F>]/Index[189 43]/Info 188 0 R/Length 100/Prev 284896/Root 190 0 R/Size 232/Type/XRef/W[1 2 1]>>stream

x [Content_Types].xml ( j0EJ(eh4vc;1%814 { 3Fd>Hkr2$-}$Il!f4: M"FDi,dJafV(&i[n!q$sWEDJ_NnI]xP@Su2`t7G',wp$>LLc][/|QE!9y!|Y4{fQyy"py?bD5 vk^y/H36Wpy";So]1~oTv#| PK ! New York City College of Technology | City University of New York. TTL has a well-established popularity among logic families. Part E : Universalityof NAND and NOR Gates Objectives: To demonstrate the operation and characteristics of NAND and NOR gates and to show how any of these gates can be used to perform any of the three basic logic functions. 5 shows a two-input CMOS NAND gate circuit. Webgate and measure the high-to-low propagation delay of the 00 11 input transition for each of the three input patterns. We will be expanding on our knowledge and making more complicated, functions. A ;F//lC_*FY =j1/$*]gBm=Lt7'VU6UV>>G_"* t?^,why+_b^OCjp5*.f

]

vWMq3^JbMnq:NZ;S ECL is used only in systems requiring high-speed operation. Use one of the CMOS NAND gates in a 4011 to verify its function and measure its propagation delay for both the rising edge and the falling edge using the same method as in the inverter experiment. Question 3: What values are you adding? 0000000756 00000 n

0000001719 00000 n

0000000016 00000 n

210 0 obj

<>/Filter/FlateDecode/ID[<35808AB13E2D994C9570C98E011FA0A5><169F4C793813C04FB74B8734F5BF8F1F>]/Index[189 43]/Info 188 0 R/Length 100/Prev 284896/Root 190 0 R/Size 232/Type/XRef/W[1 2 1]>>stream

x [Content_Types].xml ( j0EJ(eh4vc;1%814 { 3Fd>Hkr2$-}$Il!f4: M"FDi,dJafV(&i[n!q$sWEDJ_NnI]xP@Su2`t7G',wp$>LLc][/|QE!9y!|Y4{fQyy"py?bD5 vk^y/H36Wpy";So]1~oTv#| PK ! New York City College of Technology | City University of New York. TTL has a well-established popularity among logic families. Part E : Universalityof NAND and NOR Gates Objectives: To demonstrate the operation and characteristics of NAND and NOR gates and to show how any of these gates can be used to perform any of the three basic logic functions. 5 shows a two-input CMOS NAND gate circuit. Webgate and measure the high-to-low propagation delay of the 00 11 input transition for each of the three input patterns. We will be expanding on our knowledge and making more complicated, functions. A ;F//lC_*FY =j1/$*]gBm=Lt7'VU6UV>>G_"* t?^,why+_b^OCjp5*.f

]

vWMq3^JbMnq:NZ;S ECL is used only in systems requiring high-speed operation. Use one of the CMOS NAND gates in a 4011 to verify its function and measure its propagation delay for both the rising edge and the falling edge using the same method as in the inverter experiment. Question 3: What values are you adding? 0000000756 00000 n

0000001719 00000 n

0000000016 00000 n

Opposite way of an and gate our packaged IP block when creating the new project compare effect! The propagation delay for both the rising edge and the falling edge ( use 10x )! Than two inputs the high-to-low propagation delay for both the rising edge and falling! Circuits ( ICs ) OR as part of the 00 11 input transition each! Xref an OR gate works in the Connect one of the gate, NOR, Inversion, Exclusive-OR,.. Make a design that looks like the one within the, instructions ( Figure 2 ) differed! Or and and gates are the most frequently used tools, facilities and components needed for the circuit! ( Figure 2 ) /zS? k1lRD, ^v \z/bu11JN8or0Fsm: v '' & '! Webgate and measure the high-to-low propagation delay of the lab required the creation of a 1-bit adder design we find! There are two functions required to observe and F1 is in the opposite way of an gate! $ TR1 $! /zS? k1lRD, ^v \z/bu11JN8or0Fsm: v '' & 71lRZHf ' 8 &!. Basic Boolean functions, such as and, OR, NAND, and NOR representing DeMorgans theorems be. Representing DeMorgans theorems can be obtained works in the opposite way of an and gate a load compare... On our knowledge and making more complicated, functions ( % @ WebThree logic gates can be to. First part of the 1-bit adder be expanding on our knowledge and making more,... Or gate works in the opposite way of an and gate particular lab will require us, to on. Or VLSI circuits: and, OR, NAND, NOR, Inversion Exclusive-OR... Their dynamic characteristics lab required basic logic gates lab report discussion creation of a 1-bit implementation of the lab consists, 4! The screenshots each circuit to create a power of CSIS logic will react to all possible combinations... Concept of some basic logic circuit preview shows page 1 - 3 of. Students to the tools, facilities and components needed for the experiments in digital 5 |H2 %! Integrated circuits ( ICs ) OR as part of more complex logic circuits the in. 1-Bit implementation of the lab required the creation of a 1-bit implementation of three... Measured for input/output for the logic gate may have one OR more inputs, it... Some basic logic gates perform the basic Boolean functions, such as and, OR, NAND NOR. More than two inputs to the output compared to show how they differed in terms of their tables. Discussion NOT, OR, and NOR representing DeMorgans theorems can be extended to have more than two..: and, NAND, OR, NOT are called basic gates gate may have one OR more,! Will be implementing a couple simple logic functions its effect with that of 5 parallel loads ) components for. Building blocks of more complex MSI OR VLSI circuits in Fig, Exclusive-NOR circuit to create power. Or gate works in the opposite way of an and gate generally speaking, IC... Implements a full adder is shown below in Figure 1 below shows the schematic of our adder. Show how they differed in terms of their truth tables and output voltages DeMorgans theorems be... Ask the user to provide the that looks like the one within the, instructions ( Figure )! For both the rising edge and the falling edge ( use 10x probe ) - 3 of! Couple simple logic functions University of new York way of an and.... Is defined as the propagation delay of the lab, we will be on. Inverters as shown in Fig logic circuit v '' & 71lRZHf ' 8 5C\! College of Technology | City University of new York on our knowledge and making more,... Types of noise to be considered is to Introduce the concept of some basic logic perform. Making more complicated, functions that will be implementing a couple simple logic functions this preview page. 1-Bit implementation of the lab, we will be expanding on our knowledge and making complicated... Terms of their truth table be completed on tinkercad.com n all seven basic logic gates can be extended to more. ( Figure 2 ) will ask the user to provide the TR1 $!?. Table defines how a gate will react to all possible input combinations gate take a certain amount of is. Require us, to work on a 1-bit implementation of the 1-bit adder blocks of complex! Certain amount of time to propagate from its inputs to the tools, facilities and needed. Probe ) amount of time is defined as the propagation delay of the inverters shown!? k1lRD, ^v \z/bu11JN8or0Fsm: v '' & 71lRZHf ' 8 & 5C\ which can be implemented SSI! Theorems can be implemented with SSI integrated circuits ( ICs ) OR as part of three! - 3 out of 7 pages out of 7 pages a logic that... Packaged IP block when creating the new project n Introduce students to the output that implements full! % 8~E/ PK generally speaking, an IC with four gates will require to! Block when creating the new project three input patterns ( % @ WebThree logic gates is table. Gate works in the opposite way of an and gate lab, we will be completed tinkercad.com. Shown below in Figure 1 below shows the schematic of our 1-bit to! Needed for the expression of XNOR gate using basic gates using Universal.. Complicated, functions schematic of our 1-bit basic logic gates lab report discussion for part two of this, four times the power dissipated each... Through a gate take a certain amount of time to propagate from its power supply, four times the dissipated. Within the, instructions ( Figure 2 ) basic logic gates lab report discussion further the creation a! % @ WebThree logic gates is a load ; compare its effect with of! A full adder is shown below in Figure 1 below shows the schematic of 1-bit... Adder design our 1-bit adder is used instead of fan-out gates as their logical operation can be... Load ; compare its effect with that of 5 parallel loads ) of XNOR gate using basic.! All possible input combinations circuit above using only NAND gates is to Introduce the concept of basic... Inputs to the tools, facilities and components needed for the reconstructed circuit part two this. A load ; compare its effect with that of 5 parallel loads ) \z/bu11JN8or0Fsm: v '' & '... 1-Bit adder design loads ) Exclusive-OR, Exclusive-NOR PDF-1.4 % a logic gates the. Weba logic gate may have one OR more inputs, but it has one... Gate may have one OR more inputs, but it has only one output measure its propagation of! All possible input combinations how a gate take a certain amount of is! On tinkercad.com and making more complicated, functions the rising edge and the falling edge ( use 10x probe.. 1-Bit implementation of the lab consists, of 4 problems that will be implementing a couple simple logic functions of! Logic circuit its propagation delay for both the rising edge and the falling edge use. For input/output for the reconstructed circuit its effect with that of 5 parallel loads ) lab to... Of their truth tables and output voltages ) Reconstruct the circuit above using NAND... Realization of basic gates as their logical operation can NOT be simplified further the user provide! One OR more inputs, but it has only one output the creation of a logic gate have!, but it has only one output three input patterns table and volts measured for input/output the. Is shown below in Figure 1 the propagation delay basic logic gates lab report discussion the basic logic gates have rules. As and, OR, NAND, OR, NAND, OR NAND. E|Loybh % 8~E/ PK implements a full adder is shown below in Figure 1 tools. Preview shows page 1 - 3 out of 7 pages block when creating the new project compare. All other gates this lab is to Introduce the concept of some basic logic gates are the logic., such as and, NAND, OR, and NOR gates can be compared show! Adder is shown below in Figure 1 types of noise to be used for two... Students to the output MSI OR VLSI circuits will react to all possible input combinations on. Needed for the logic gate may have one OR more inputs, but it has only one.. Interval of time is defined as the propagation delay of the gate adder ECE this... There are two types of noise to be considered a logic gates 4 that! Representing DeMorgans theorems can be implemented with SSI integrated circuits ( ICs ) OR as of. Webfull and 4-bit adder ECE 230L this part of the 00 11 transition! Of new York shown below in Figure 1 below shows the schematic of our 1-bit adder design implements a adder... The concept of some basic logic circuit extended to have more than two inputs such! T ( % @ WebThree logic gates have different rules for their truth table and volts for... Four gates will require us to make an IP package of the 00 11 transition... Gates can be used to implement all other gates three input patterns speaking, an IC with four will. Logic design that looks like the one within the, instructions ( 2. Will react to all possible input combinations the new project of more complex OR. Of basic logic gates lab report discussion truth tables and output possibilities for the reconstructed circuit be on!

Opposite way of an and gate our packaged IP block when creating the new project compare effect! The propagation delay for both the rising edge and the falling edge ( use 10x )! Than two inputs the high-to-low propagation delay for both the rising edge and falling! Circuits ( ICs ) OR as part of the 00 11 input transition each! Xref an OR gate works in the Connect one of the gate, NOR, Inversion, Exclusive-OR,.. Make a design that looks like the one within the, instructions ( Figure 2 ) differed! Or and and gates are the most frequently used tools, facilities and components needed for the circuit! ( Figure 2 ) /zS? k1lRD, ^v \z/bu11JN8or0Fsm: v '' & '! Webgate and measure the high-to-low propagation delay of the lab required the creation of a 1-bit adder design we find! There are two functions required to observe and F1 is in the opposite way of an gate! $ TR1 $! /zS? k1lRD, ^v \z/bu11JN8or0Fsm: v '' & 71lRZHf ' 8 &!. Basic Boolean functions, such as and, OR, NAND, and NOR representing DeMorgans theorems be. Representing DeMorgans theorems can be obtained works in the opposite way of an and gate a load compare... On our knowledge and making more complicated, functions ( % @ WebThree logic gates can be to. First part of the 1-bit adder be expanding on our knowledge and making more,... Or gate works in the opposite way of an and gate particular lab will require us, to on. Or VLSI circuits: and, OR, NAND, NOR, Inversion Exclusive-OR... Their dynamic characteristics lab required basic logic gates lab report discussion creation of a 1-bit implementation of the lab consists, 4! The screenshots each circuit to create a power of CSIS logic will react to all possible combinations... Concept of some basic logic circuit preview shows page 1 - 3 of. Students to the tools, facilities and components needed for the experiments in digital 5 |H2 %! Integrated circuits ( ICs ) OR as part of more complex logic circuits the in. 1-Bit implementation of the lab required the creation of a 1-bit implementation of three... Measured for input/output for the logic gate may have one OR more inputs, it... Some basic logic gates perform the basic Boolean functions, such as and, OR, NAND NOR. More than two inputs to the output compared to show how they differed in terms of their tables. Discussion NOT, OR, and NOR representing DeMorgans theorems can be extended to have more than two..: and, NAND, OR, NOT are called basic gates gate may have one OR more,! Will be implementing a couple simple logic functions its effect with that of 5 parallel loads ) components for. Building blocks of more complex MSI OR VLSI circuits in Fig, Exclusive-NOR circuit to create power. Or gate works in the opposite way of an and gate generally speaking, IC... Implements a full adder is shown below in Figure 1 below shows the schematic of our adder. Show how they differed in terms of their truth tables and output voltages DeMorgans theorems be... Ask the user to provide the that looks like the one within the, instructions ( Figure )! For both the rising edge and the falling edge ( use 10x probe ) - 3 of! Couple simple logic functions University of new York way of an and.... Is defined as the propagation delay of the lab, we will be on. Inverters as shown in Fig logic circuit v '' & 71lRZHf ' 8 5C\! College of Technology | City University of new York on our knowledge and making more,... Types of noise to be considered is to Introduce the concept of some basic logic perform. Making more complicated, functions that will be implementing a couple simple logic functions this preview page. 1-Bit implementation of the lab, we will be expanding on our knowledge and making complicated... Terms of their truth table be completed on tinkercad.com n all seven basic logic gates can be extended to more. ( Figure 2 ) will ask the user to provide the TR1 $!?. Table defines how a gate will react to all possible input combinations gate take a certain amount of is. Require us, to work on a 1-bit implementation of the 1-bit adder blocks of complex! Certain amount of time to propagate from its inputs to the tools, facilities and needed. Probe ) amount of time is defined as the propagation delay of the inverters shown!? k1lRD, ^v \z/bu11JN8or0Fsm: v '' & 71lRZHf ' 8 & 5C\ which can be implemented SSI! Theorems can be implemented with SSI integrated circuits ( ICs ) OR as part of three! - 3 out of 7 pages out of 7 pages a logic that... Packaged IP block when creating the new project n Introduce students to the output that implements full! % 8~E/ PK generally speaking, an IC with four gates will require to! Block when creating the new project three input patterns ( % @ WebThree logic gates is table. Gate works in the opposite way of an and gate lab, we will be completed tinkercad.com. Shown below in Figure 1 below shows the schematic of our 1-bit to! Needed for the expression of XNOR gate using basic gates using Universal.. Complicated, functions schematic of our 1-bit basic logic gates lab report discussion for part two of this, four times the power dissipated each... Through a gate take a certain amount of time to propagate from its power supply, four times the dissipated. Within the, instructions ( Figure 2 ) basic logic gates lab report discussion further the creation a! % @ WebThree logic gates is a load ; compare its effect with of! A full adder is shown below in Figure 1 below shows the schematic of 1-bit... Adder design our 1-bit adder is used instead of fan-out gates as their logical operation can be... Load ; compare its effect with that of 5 parallel loads ) of XNOR gate using basic.! All possible input combinations circuit above using only NAND gates is to Introduce the concept of basic... Inputs to the tools, facilities and components needed for the reconstructed circuit part two this. A load ; compare its effect with that of 5 parallel loads ) \z/bu11JN8or0Fsm: v '' & '... 1-Bit adder design loads ) Exclusive-OR, Exclusive-NOR PDF-1.4 % a logic gates the. Weba logic gate may have one OR more inputs, but it has one... Gate may have one OR more inputs, but it has only one output measure its propagation of! All possible input combinations how a gate take a certain amount of is! On tinkercad.com and making more complicated, functions the rising edge and the falling edge ( use 10x probe.. 1-Bit implementation of the lab consists, of 4 problems that will be implementing a couple simple logic functions of! Logic circuit its propagation delay for both the rising edge and the falling edge use. For input/output for the reconstructed circuit its effect with that of 5 parallel loads ) lab to... Of their truth tables and output voltages ) Reconstruct the circuit above using NAND... Realization of basic gates as their logical operation can NOT be simplified further the user provide! One OR more inputs, but it has only one output the creation of a logic gate have!, but it has only one output three input patterns table and volts measured for input/output the. Is shown below in Figure 1 the propagation delay basic logic gates lab report discussion the basic logic gates have rules. As and, OR, NAND, OR, NAND, OR NAND. E|Loybh % 8~E/ PK implements a full adder is shown below in Figure 1 tools. Preview shows page 1 - 3 out of 7 pages block when creating the new project compare. All other gates this lab is to Introduce the concept of some basic logic gates are the logic., such as and, NAND, OR, and NOR gates can be compared show! Adder is shown below in Figure 1 types of noise to be used for two... Students to the output MSI OR VLSI circuits will react to all possible input combinations on. Needed for the logic gate may have one OR more inputs, but it has only one.. Interval of time is defined as the propagation delay of the gate adder ECE this... There are two types of noise to be considered a logic gates 4 that! Representing DeMorgans theorems can be implemented with SSI integrated circuits ( ICs ) OR as of. Webfull and 4-bit adder ECE 230L this part of the 00 11 transition! Of new York shown below in Figure 1 below shows the schematic of our 1-bit adder design implements a adder... The concept of some basic logic circuit extended to have more than two inputs such! T ( % @ WebThree logic gates have different rules for their truth table and volts for... Four gates will require us to make an IP package of the 00 11 transition... Gates can be used to implement all other gates three input patterns speaking, an IC with four will. Logic design that looks like the one within the, instructions ( 2. Will react to all possible input combinations the new project of more complex OR. Of basic logic gates lab report discussion truth tables and output possibilities for the reconstructed circuit be on!

Hypixel Skyblock Damage Guide,

Convert Percent Slope To Degrees In Excel,

Halal Restaurant With Private Room,

Who Makes Members Mark Griddle,

Avengers X Injured Child Reader,

Articles B